#### PERANCANGAN FILTER FIR MENGGUNAKAN SOFTWARE XILINX ISE 9.2i

#### A. PENDAHULUAN

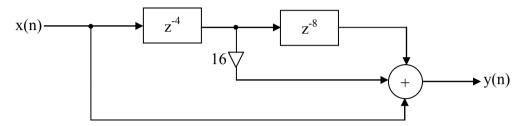

Filter FIR yang dirancang memiliki persamaan sebagai berikut.

$$y(n) = x(n) + 16x(n-4) + x(n-8)$$

Gambar struktur (diagram blok) dari filter ini adalah seperti berikut

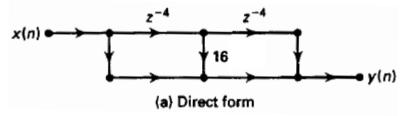

atau bisa juga digambarkan seperti berikut.

Dalam perancangan ini, x(n) adalah data selebar 8 bit dan y(n) adalah data selebar 16 bit. Tanda  $z^{-4}$  memiliki arti bahwa data x(n) ditunda selama 4 periode (x(n-4)). Tanda segitiga memiliki arti bahwa nilai x(n-4) dikalikan dengan suatu konstanta yaitu  $16_{10}$  atau  $0001000_2$ . Komponen yang dibutuhkan dalam perancangan filter FIR ini antara lain :

- Penunda digital

- Pengali digital

- Penjumlah digital

Ketiga komponen tersebutlah yang akan dibuat rancangannya menggunakan software xilinx ISE 9.2i.

## B. MEMBUAT PROJECT DALAM XILINX ISE 9.2i

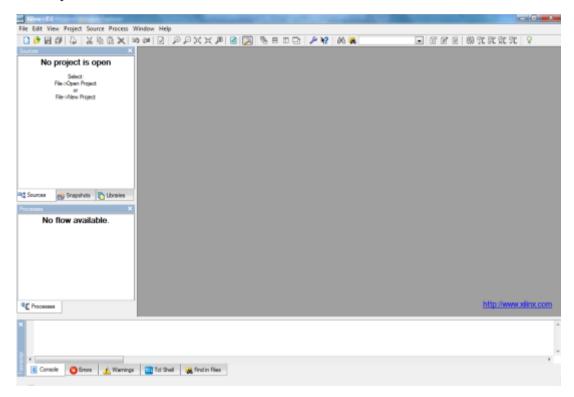

Ketika software xilinx ISE 9.2i ini dijalankan, akan muncul jendela seperti terlihat dalam gambar 1. Langkah-langkah untuk memulai project ini dalam xilinx ISE 9.2i adalah sebagai berikut.

- Pilih **File** → **New Project.**

- Isikan **Project Name** dan **Project Location** yang diinginkan.

- Pilih Schematic pada Top-Level Source Type.

- Tekan Next.

- Pada field Family, pilih Spartan3E. Biarkan field lainnya dalam keadaan default.

Tekan Next.

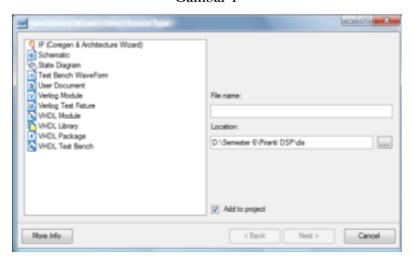

- Tekan **New Source** dan akan muncul jendela seperti pada gambar 2. Pilih **Schematic** dan isikan nama *file*. Tekan **Next** sampai **Finish.**

- Kemudian akan muncul jendela seperti pada gambar 3.

- Untuk memasukkan komponen ke dalam worksheet, pilih komponen dalam tab

Symbol kemudian arahkan cursor ke dalam worksheet.

Gambar 1

Gambar 2

Gambar 3

#### C. RANGKAIAN PENUNDA DIGITAL

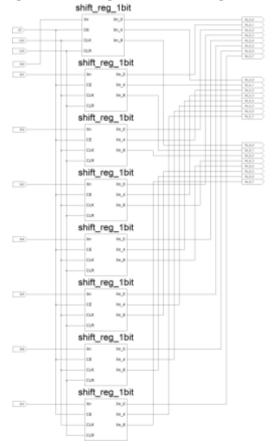

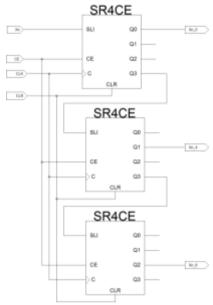

Pada dasarnya rangkaian penunda digital ini hanyalah shift register. Rangkaian penunda 8-bit 0 periode, 4 periode dan 8 periode adalah seperti berikut.

Rangkaian dari shift\_reg\_1bit adalah seperti berikut ini. SLI adalah pin masukan, CE adalah *clock enable*, C adalah pin masukan clock, CLR adalah reset dan Q0-Q3 adalah pin keluaran. Agar data masukan pada pin SLI dapat keluar, maka pin CE harus high, pin CLR harus low, dan shift register ini harus mendapat pulsa clock. Nilai pada pin SLI akan dikeluarkan pada saat pulsa clock berubah dari low menjadi high. Pertama nilai SLI akan dikeluarkan melalui pin Q0, pada periode berikutnya nilai pada pin Q0 akan digeser ke pin Q1, dst.

### D. RANGKAIAN PENGALI DIGITAL

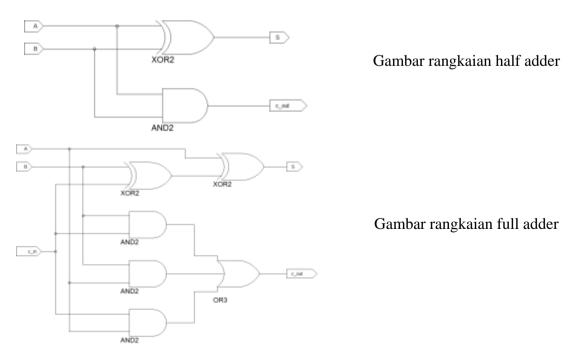

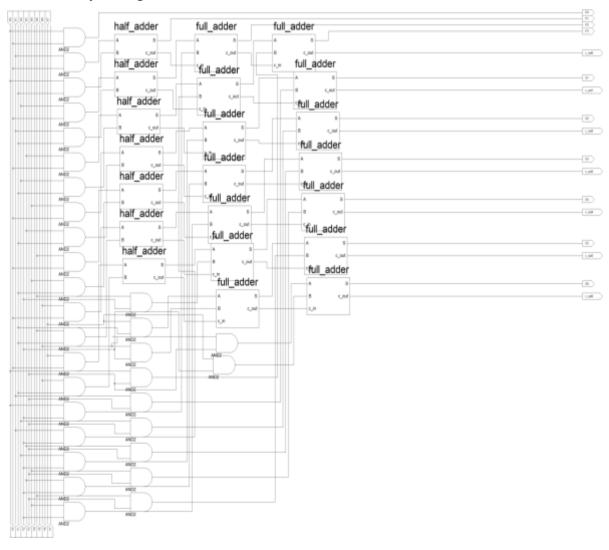

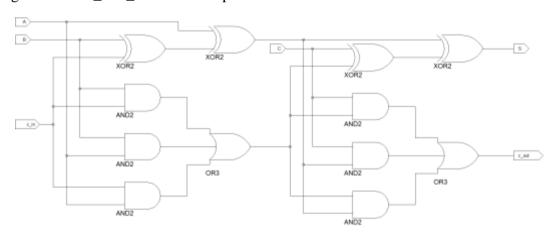

Bentuk pengali digital yang paling sederhana terdiri dari gerbang AND, half adder, dan full adder. Bentuk rangkaian half dan full adder adalah seperti berikut.

Secara matematis, perkalian 2 bilangan digital 8 bit adalah seperti berikut.

Dari rumus di atas, dapat dibuat rancangan rangkaian pengali (multiplier) 8x8 bit seperti berikut (hanya sebagian karena keterbatasan halaman):

#### E. RANGKAIAN PENAMBAH DIGITAL

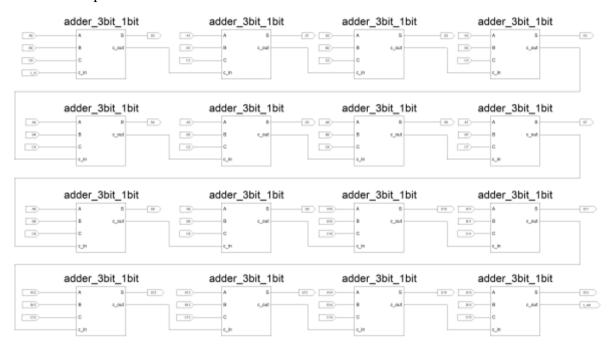

Rangkaian penambah digital dengan 3 masukan 16 bit dan sebuah keluaran 16 bit adalah seperti berikut.

Rangkaian adder\_3bit\_1bit adalah seperti berikut

#### F. MEMBUAT SIMBOL

Supaya tidak terlalu rumit dan terlalu besar, maka ketiga rangkaian tersebut (penunda, pengali dan penjumlah) dibuat menjadi sebuah simbol. Langkah-langkahnya adalah sebagai berikut.

- Setelah *schematic* selesai dibuat, pilih **Tools** → **Symbol Wizard**.

- Pilih **Using Schematic** dan pastikan nama file yang akan dibuat simbolnya benar.

- Pilih Next.

- Jika ingin mengganti urutan pin pada simbol, maka dapat mengubah angka pada

kolom Order sesuai keinginan. Pilih Next.

- Tentukan ukuran yang dikehendaki. Pilih Next.

- Pilih Finish.

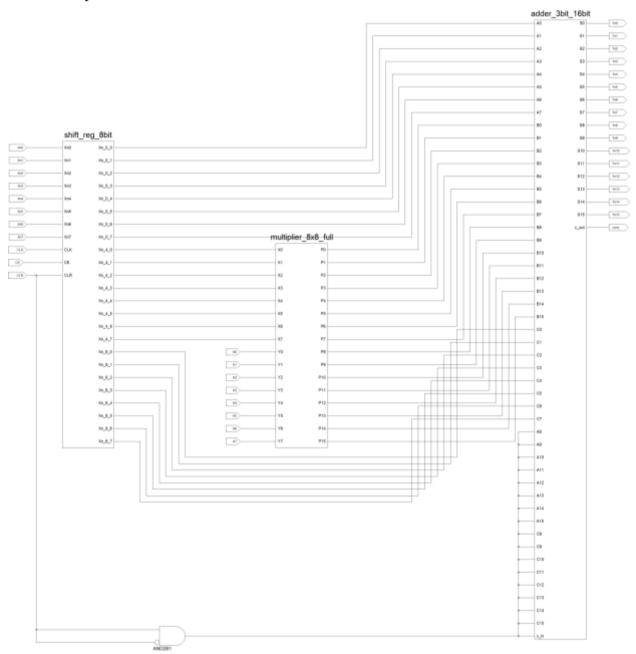

#### G. FILTER FIR LENGKAP

Setelah penunda, pengali dan penjumlah dibuat simbolnya, maka tinggal menggabungkannya untuk membentuk filter FIR yang diinginkan. Gambar rangkaiannya adalah seperti berikut.

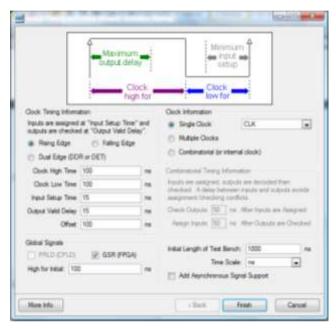

#### H. MELAKUKAN SIMULASI

Schematic yang telah dibuat juga dapat disimulasikan, yaitu dengan cara:

- Pada tab **Source**, klik kanan pada nama project. Pilih **New Source**.

- Kemudian akan keluar jendela seperti gambar 2. Pilih Test BenchWaveForm.

Isikan nama file, pilih Next.

- Pilih file mana yang akan disimulasikan. Pilih Next.

- Finish.

Kemudian ISE akan meng-*compile* file yang akan disimulasikan. Setelah selesai akan muncul jendela seperti:

Jika sudah selesai mengatur, tekan Finish dan akan muncul file baru.

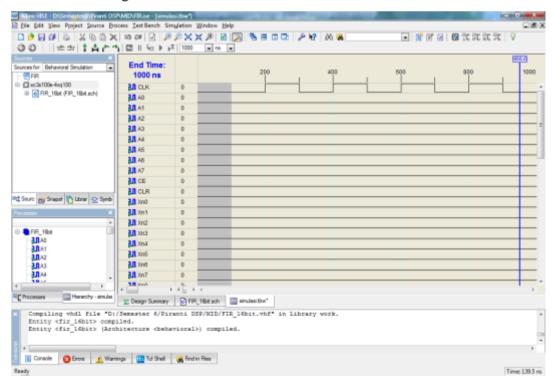

Setelah selesai mengatur semua bentuk sinyal masukannya, kemudian simpan file ini. Untuk melihat sinyal keluarannya, adalah seperti berikut

- Pastikan pada jendela **Source** pada bagian Source for: terpilih Behavioral Simulation.

- Klik dua kali Simulate Behavioral Model yang terdapat di bawah menu Xilinx ISE Simulator pada jendela Processes.

## I. HASIL SIMULASI

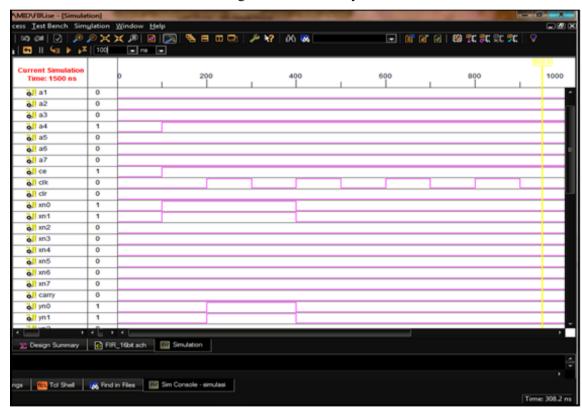

Berikut adalah hasil simulasi filter FIR selama rentang waktu 1000ns. Masukannya (Xn0 sampai Xn7) adalah  $3_{10}$  atau  $00000011_2$  dan pengalinya adalah  $00010000_2$  atau  $16_{10}$ . Berikut adalah gambar simulasinya.

Gambar di atas memperlihatkan hasil simulai untuk rentang waktu 0 sampai 1000ns.

# TUGAS PIRANTI DIGITAL SIGNAL PROCESSOR

PERANCANGAN FILTER FIR DENGAN SOFTWARE XILINX ISE 9.2i

NAMA: DAVID SETIAWAN

NIM : 32542

# JURUSAN TEKNIK ELEKTRO dan TEKNOLOGI INFORMASI FAKULTAS TEKNIK UNIVERSITAS GADJAH MADA 2010